超大规模集成电路设计基础 软件开发的核心地位与实践

在超大规模集成电路(VLSI,Very Large Scale Integration)的设计流程中,软件开发并非辅助工具,而是贯穿始终的核心驱动力与实现基石。从概念定义到物理实现,现代VLSI设计的高度复杂性决定了其本质是一个以先进软件和算法为核心的密集型开发过程。本文将探讨VLSI设计流程中软件开发的基本概念、关键工具及其核心作用。

一、 软件驱动的设计范式

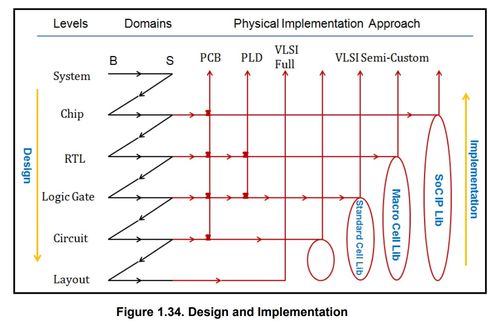

传统的硬件设计已演变为“软件定义硬件”的范式。设计起点通常是使用硬件描述语言(HDL),如Verilog或VHDL,进行寄存器传输级(RTL)建模。这一阶段本质上即是软件开发,工程师编写代码来描述电路的功能、数据流和控制逻辑。代码的质量(可读性、可综合性和可验证性)直接决定了后续所有环节的效率和芯片最终性能。高级综合(HLS)工具的出现,进一步允许使用C/C++等更抽象的软件语言进行行为级描述,再由工具自动转换为RTL代码,提升了设计抽象层次和开发效率。

二、 核心设计工具链(EDA软件)

整个VLSI设计流程依赖于一套庞大的电子设计自动化(EDA)软件工具链,每一环节都对应着专门的软件:

- 设计与仿真:

- HDL仿真器(如ModelSim, VCS):用于对RTL代码进行功能仿真,验证逻辑正确性,是芯片的“软件调试”阶段。

- 逻辑综合工具(如Design Compiler):将RTL代码“编译”成基于特定工艺库的门级网表,实现从行为描述到物理逻辑的转换。

- 验证:

- 形式验证工具:数学上证明设计等价性或属性正确,无需测试向量。

- 硬件仿真器和FPGA原型验证平台:通过运行实际软件或大量测试来加速验证,其配置、编译和调试严重依赖配套软件。

- 通用验证方法学(UVM):基于SystemVerilog的标准化验证框架,极大地提高了验证代码的重用性和验证效率。

- 物理实现:

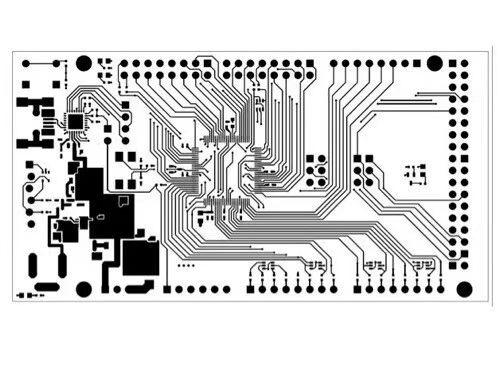

- 布局布线工具(如Innovus, ICC2):将门级网表转换成实际的物理版图,决定晶体管和连线的几何形状与位置。这是一个计算极度密集的优化过程,算法(如布局、布线、时序优化算法)是工具的灵魂。

- 签核工具:进行静态时序分析(STA)、功耗分析、物理验证(DRC, LVS)等,确保设计符合时序、功耗和制造规则。

三、 软件开发技能的关键要求

VLSI设计工程师所需的软件开发能力远超一般认知:

- 编程语言:精通Verilog/VHDL是基础,掌握SystemVerilog(用于验证)、Tcl(用于工具控制)、Python/Perl(用于脚本自动化)和C++(用于算法理解或HLS)已成为必备技能。

- 算法与数据结构:理解EDA工具背后的算法(如图论、优化算法)有助于更高效地使用工具并解决复杂问题。

- 软件工程方法:版本控制(Git)、模块化设计、代码复用、自动化脚本编写等实践,对于管理数百万行代码的设计和验证环境至关重要。

- 系统级建模:随着芯片-软件协同设计(Co-design)的重要性提升,使用SystemC等进行虚拟原型开发,在芯片流片前进行软件开发和系统验证,已成为关键环节。

四、 挑战与趋势

面对工艺演进至纳米尺度以及系统级芯片(SoC)的复杂性爆炸,VLSI设计软件面临巨大挑战:处理海量数据、缩短迭代周期、保证低功耗和高性能。未来趋势集中在:

- 人工智能与机器学习:将AI/ML技术集成到EDA工具中,用于预测设计结果、自动优化布局布线、加速验证收敛等。

- 云化与协作平台:设计平台向云端迁移,支持分布式计算、数据共享和全球团队协作。

- 更高层次抽象:继续提升设计抽象层次,向系统级、领域专用语言(DSL)发展,以应对特定领域(如AI、自动驾驶)的芯片设计需求。

结论

在超大规模集成电路设计中,软件开发与硬件设计已深度融合、不可分割。从描述、验证到实现,强大的软件工具链和工程师的卓越软件开发能力,是驾驭芯片超大规模复杂性、实现创新设计并成功流片的决定性因素。掌握这一“软”核心,是通往现代VLSI设计殿堂的必由之路。

如若转载,请注明出处:http://www.6shuju.com/product/69.html

更新时间:2026-05-10 03:59:57