基于ISO/IEC 14443 Type A协议的无源电子标签数字集成电路设计

无源电子标签,作为射频识别(RFID)技术的核心组件,以其无需内置电源、成本低廉、体积小巧等优势,在门禁系统、电子支付、物流追踪等领域得到广泛应用。其中,遵循ISO/IEC 14443 Type A协议的标签,因其在近场通信(NFC)中的关键地位,其数字集成电路的设计尤为关键。本文将探讨基于该协议的无源电子标签数字集成电路的设计要点与流程。

一、系统架构与协议概述

ISO/IEC 14443 Type A协议规定了工作在13.56MHz频率下的近耦合非接触式识别卡的通信接口与协议。一个完整的无源标签数字集成电路核心通常包含以下模块:

- 射频前端与电源管理单元:负责从读写器发射的射频场中耦合能量,经整流、稳压后为芯片提供稳定的直流电源,同时解调接收到的指令信号。

- 时钟提取与生成单元:从载波中分频产生系统所需的各种时钟信号。

- 数字基带处理核心:这是设计的重中之重,负责协议的实现,包括帧解码、命令解析、状态机控制、数据加密/认证(如需要)、响应帧的编码与调制控制等。

- 存储器:通常为EEPROM或新型非易失性存储器,用于存储唯一的识别码(UID)及用户数据。

- 防冲突与安全逻辑:实现防冲突算法(如Type A的时隙ALOHA机制)及安全认证功能。

二、数字基带处理核心设计

这是实现协议合规性与功能完整性的核心。设计流程主要包括:

- 协议状态机设计:根据ISO/IEC 14443-4 Type A的通信流程,精确设计芯片上电复位、空闲、就绪、激活、停止等状态及其转换条件。状态机需稳健处理所有合规指令及异常情况。

- 编解码器设计:

- 解码:实现针对106kbps速率的改进米勒码解码,将读写器发送的调制信号还原为NRZ数据流,并进行CRC校验。

- 编码:实现对返回链路106kbps速率的曼彻斯特码编码,将待发送的NRZ数据流转换为调制控制信号,驱动负载调制电路。

- 命令解析与执行单元:对解码后的命令帧(如REQA、WUPA、SELECT、RATS等)进行解析,触发相应的操作,如读取存储器内容、执行认证过程或准备响应数据。

- 防冲突模块:实现防冲突循环,处理多标签同时在场的情况。该模块需管理标签的序列号,并在收到ANTICOLLISION命令时,根据时隙参数和自身UID做出正确的响应或静默。

- 低功耗设计:作为无源器件,功耗直接决定有效工作距离。在数字电路层面,需广泛采用门控时钟、多阈值电压、操作数隔离、状态保持等低功耗设计技术,确保在满足时序要求下动态和静态功耗最小化。

三、设计流程与验证挑战

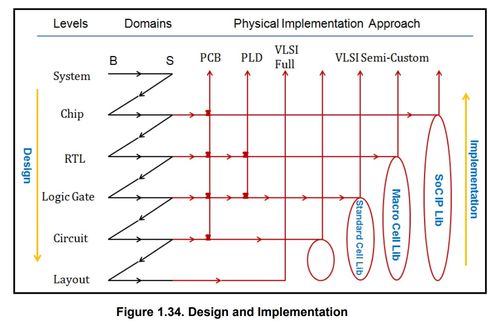

- 前端设计与仿真:使用硬件描述语言(如Verilog或VHDL)进行RTL级设计,并进行严格的功能仿真,确保逻辑正确性。需搭建包含协议模型、信道模型及射频前端行为模型的完整测试平台。

- 逻辑综合与优化:使用标准单元库进行逻辑综合,将RTL代码映射为门级网表。此阶段需设定严格的时序和面积约束,并优化功耗。

- 后端物理设计:包括布局规划、单元放置、时钟树综合、布线、寄生参数提取等。对于无源标签芯片,面积和成本极其敏感,布局需高度紧凑。需特别注意射频模拟部分(如整流器、解调器)与数字核心的布局隔离,防止数字开关噪声干扰敏感的模拟电路。

- 验证与测试:

- 后仿真:使用提取的寄生参数进行带时序信息的门级仿真,验证设计在真实物理条件下仍符合时序要求。

- 协议一致性验证:这是关键,需使用专业的RFID/NFC协议测试仪或搭建实测环境,确保标签与标准读写器的互操作性完全符合ISO/IEC 14443 Type A规范。

- 功耗与性能测试:实测芯片在不同场强下的启动电压、最小工作场强及最大通信距离。

四、发展趋势

随着物联网和移动支付的普及,对无源标签芯片提出了更高要求:

- 更高安全性:集成更强大的加密算法(如AES)和安全存储单元。

- 更小面积与更低功耗:采用更先进的半导体工艺节点。

- 增强功能:集成传感器接口,向“无源传感标签”发展。

- 设计自动化:使用高层次综合(HLS)和IP复用技术,缩短设计周期。

###

基于ISO/IEC 14443 Type A协议的无源电子标签数字集成电路设计,是一个涉及协议理解、低功耗数字设计、混合信号集成及严格验证的系统工程。成功的芯片设计需要在满足严苛协议标准、极低成本与面积约束以及超低功耗要求之间取得精妙平衡。随着技术的演进,这类芯片将继续向着更智能、更安全、更集成化的方向发展,为万物互联的世界提供基础支撑。

如若转载,请注明出处:http://www.6shuju.com/product/68.html

更新时间:2026-04-20 09:38:09