融合经典与前沿 国外学者基于传统集成电路技术破解量子计算三维封装瓶颈

量子计算机被视为未来计算的革命性力量,但其从实验室原型走向大规模实用化的道路上面临着诸多严峻挑战。其中,一个核心的工程难题是如何在有限的物理空间内,高效、可靠地集成与控制数量庞大且极度脆弱的量子比特(qubits),并实现其复杂的互连。来自麻省理工学院、代尔夫特理工大学等顶尖研究机构的多支团队,相继在《自然·电子学》和《科学》等顶级期刊上报告了突破性进展。他们巧妙地借鉴并改造了成熟的大规模集成电路(VLSI)设计与先进封装技术,特别是三维集成(3D-IC)与硅通孔(TSV)技术,为量子处理器的可扩展性提供了极具前景的解决方案。

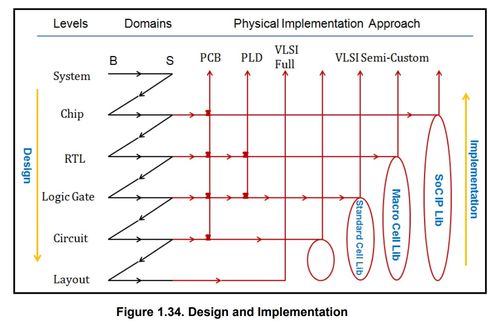

传统量子芯片的封装多采用平面二维结构,随着量子比特数量的增加,控制线、读取线等经典电子线路的布线变得异常复杂和拥挤,会引入大量噪声、串扰和热量,严重干扰量子比特的相干性。而现代高性能计算芯片(如GPU、CPU)早已采用三维堆叠封装来克服类似问题,通过在垂直方向上堆叠多层芯片并使用硅通孔实现层间垂直互联,极大地提升了集成密度和信号传输效率。

研究团队的创新之处在于,将这套经过数十年发展的成熟“工具箱”适配于量子系统。他们设计并制造了一种多层芯片架构:底层(或中间层)为包含超导量子比特的量子芯片层;在其上方或下方,通过微凸块(Microbumps)和硅通孔紧密集成一层或多层专用的CMOS控制与读取电路芯片。这种设计带来了多重关键优势:

- 空间解耦与噪声隔离:将产生热噪声和电噪声的经典控制电路与对噪声极其敏感的量子比特在物理上分离至不同芯片层,并通过优化设计(如插入屏蔽层、使用高纯度材料)最大程度地隔离噪声。极短的垂直互连(TSV)取代了长距离的平面键合线,显著减少了寄生电感和电容,提升了信号保真度与速度。

- 高密度并行控制:三维集成允许在量子比特层正上方直接布置海量的控制单元,实现“一对一”或“一对多”的精准、并行控制与读取。这解决了二维平面布线无法支持数千甚至数百万量子比特扩展的根本性瓶颈。

- 热管理与互连优化:三维结构便于设计更高效的分层热管理方案,例如将产热大的控制层靠近散热模组。TSV技术提供了高带宽、低延迟的垂直通信通道,为未来量子处理器内部及量子处理器与经典协处理器之间的高速数据交换奠定了基础。

例如,麻省理工学院团队展示了一种采用“面对面”键合的三维集成方案,将28纳米工艺的CMOS控制芯片与超导量子比特芯片直接融合。实验结果表明,该架构在保持量子比特高质量(高相干时间)的实现了对量子比特的高保真、低延迟操控,验证了技术路线的可行性。

这项跨领域的融合研究意义深远。它表明,在追逐下一代“量子计算”这一全新范式的我们不应忽视现有“经典集成电路”技术体系中蕴藏的深厚工程智慧与强大制造能力。将两者结合,为量子计算机从几十个量子比特走向实用化的百万量子比特级系统,提供了一条可制造、可扩展的工程化路径。这不仅是封装技术的突破,更是系统工程思维的胜利,有望加速全栈量子计算系统的成熟,为最终实现量子优势迈出坚实的一步。

如若转载,请注明出处:http://www.6shuju.com/product/67.html

更新时间:2026-04-20 08:09:26