数字集成电路版图设计 从Cadence IC原理图到仿真与软件开发全流程解析

数字集成电路(Digital Integrated Circuit, IC)是现代电子设备的核心,其性能、功耗和面积直接决定了产品的竞争力。版图设计作为IC设计流程中的关键一环,是将电路原理图转化为可用于芯片制造的物理布局的过程。本文将系统性地介绍数字集成电路版图设计的核心内容,重点聚焦于Cadence IC设计平台下的原理图绘制、仿真验证,以及相关的软件开发支持。

一、 Cadence IC设计平台:原理图绘制与仿真

Cadence Design Systems是全球领先的电子设计自动化(EDA)软件提供商,其Virtuoso平台是模拟和混合信号IC设计的行业标准,而其Innovus、Genus等工具则专攻数字IC设计与实现。对于数字IC的前端设计,原理图绘制和仿真验证是基础。

1. 原理图绘制

- 工具与环境:在Cadence生态中,通常使用Virtuoso Schematic Editor进行晶体管级或门级原理图的绘制。它为设计师提供了直观的图形界面,用于放置和连接标准单元、定制模块、晶体管、电阻、电容等元器件。

- 设计层次化:支持层次化设计是大型数字IC设计的关键。设计师可以创建模块(Block),将其作为子电路在更高层次中复用,这极大地提高了设计效率和可维护性。

- 设计规则与连接性检查:在绘制过程中,工具会实时进行电气连接性检查和基本的设计规则检查,帮助发现短路、开路等低级错误。

2. 电路仿真

- 仿真引擎:Cadence提供强大的仿真工具,如Spectre、APS(Accelerated Parallel Simulator)和UltraSim。对于数字电路,虽然门级仿真常使用数字仿真器(如Xcelium),但在混合信号设计或需要高精度分析时,这些模拟仿真器至关重要。

- 仿真流程:设计师在原理图中定义激励信号(如时钟、数据输入)、设置仿真类型(瞬态分析、直流分析、交流分析等),然后运行仿真。仿真的目的是验证电路在预设条件下的功能正确性、时序性能和功耗特性。

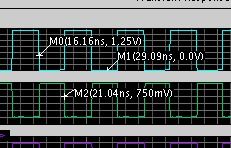

- 结果分析:通过Virtuoso Visualization & Analysis (WaveView) 等工具,设计师可以直观地查看信号波形、测量延迟、建立/保持时间等关键参数,并与设计规范进行比对。

二、 从原理图到版图:设计实现流程

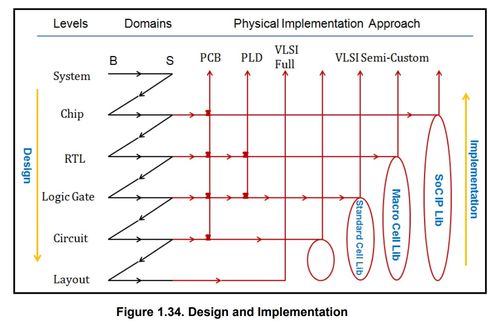

原理图验证通过后,设计便进入物理实现阶段。对于数字IC,这通常是一个自动化的流程,称为RTL-to-GDSII流程。

- 逻辑综合:使用工具(如Cadence Genus)将硬件描述语言(如Verilog/VHDL)描述的寄存器传输级(RTL)设计,在特定工艺库(标准单元库、IO库等)的约束下,转换为门级网表。这个网表在功能上与原理图等价,但包含了具体的标准单元实例。

- 布局规划与电源规划:确定芯片的整体形状、模块位置以及全局电源/地线网络,这对芯片的性能、可靠性和可制造性至关重要。

- 布局与布线:使用物理实现工具(如Cadence Innovus)自动进行标准单元的放置和单元间的信号线连接(布线)。此阶段必须严格遵守Foundry提供的物理设计规则(DRC)和电学设计规则(ERC)。

- 时序与功耗签核:在布局布线后,需进行精确的静态时序分析(STA,使用Tempus工具)和功耗分析,确保最终设计满足时序和功耗目标。

- 物理验证:对生成的版图(GDSII格式)进行设计规则检查(DRC)、版图与原理图一致性检查(LVS)以及天线效应检查等。Calibre是行业常用的物理验证工具,可与Cadence流程紧密集成。

三、 软件开发在版图设计中的关键作用

现代IC设计离不开强大的软件支持,这不仅仅指EDA工具本身,还包括支撑设计流程的定制化软件开发。

- 设计流程自动化脚本:由于IC设计流程步骤繁多,工程师常使用脚本语言(如Tcl、Perl、Python)来自动化重复性任务,例如批量仿真、结果收集与报告生成、文件格式转换等。Cadence工具普遍支持Tcl作为控制和扩展语言。

- 定制化工具与插件开发:针对特定的设计需求或工艺,设计团队可能需要开发定制工具或为现有EDA工具编写插件(SKILL语言是Cadence平台的专用扩展语言),以实现特殊检查、数据提取或流程集成,从而提升设计效率和准确性。

- 设计数据管理与版本控制:类似于软件工程,大型IC设计项目需要管理海量的设计文件(RTL代码、约束文件、仿真脚本、版图数据等)。集成版本控制系统(如Git)和设计数据管理(DM)软件对于团队协作、设计可追溯性和项目进度管理不可或缺。

- 工艺设计套件开发与维护:PDK是连接芯片设计公司与晶圆代工厂的桥梁。PDK的开发与维护本身就是一项复杂的软件工程,它包含了工艺文件、规则文件、器件模型、标准单元库及其视图(符号、原理图、版图、抽象)等,所有这些都需要通过软件来创建、验证和集成到设计流程中。

###

数字集成电路版图设计是一个集电路理论、半导体工艺和计算机软件技术于一体的高度复杂的工程领域。Cadence IC平台提供了从原理图捕获、仿真验证到物理实现的完整解决方案。而熟练运用这些工具,并结合高效的软件开发实践来自动化流程、解决特定问题,是现代数字IC设计师提升竞争力、应对日益严峻的设计挑战的必备技能。从一张清晰的功能原理图到一块可制造的高性能芯片版图,每一步都凝结着设计与软件的深度融合。

如若转载,请注明出处:http://www.6shuju.com/product/64.html

更新时间:2026-04-14 07:50:56